# 2013 International SoC Design Conference

**Conference Information**

**Papers**

**Sponsors**

Sponsored by

http://www.isocc.org

Copyright and Reprint Permission: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limit of U.S. copyright law for private use of patrons those articles inthis volume that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid through Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923. Forother copying, reprint or republication permission, write to IEEE Copyrights Manager, IEEE Operations Center, 445 Hoes Lane, Piscataway, NJ 08854. All rights reserved. Copyright ©2013 by IEEE.

# 2013 International SoC Design Conference

| CDC(D)-001 | Multiple-Output Switched-Capacitor DC-DC Converter with Digital Capacitance Modulation  Jeongyun Lee, Sunwoo Yoon and Donghyun Baek  Chung-Ang University, Korea 172                                                                                |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CDC(D)-002 | A 5.6Gb/s CMOS CDR IC with a static phase offset compensated linear phase detector Chung Hwan Son and Sangjin Byun Dongguk University, Korea 178                                                                                                    |

| CDC(D)-003 | A 12 Gb/s 0.92mW/Gb/s Forwarded Clock Receiver with Low Jitter tracking Bandwidth Variation in 65nm CMOS  Young-Ju Kim and Lee-Sup Kim  Korea Advanced Institute of Science and Technology (KAIST), Korea                                           |

| CDC(D)-004 | Effect of Signal Selection Algorithm on the FPN Characteristics in a Two Step Charge Transfer Linear-logarithmic APS Inkyu Baek, Jiwon Lee, Seungmin Baek and Kyounghoon Yang Korea Advanced Institute of Science and Technology (KAIST), Korea 180 |

| CDC(D)-005 | A C-band Bi-directional T/R Chipset in 0.18 µm CMOS Technology  Moon-Kyu Cho, Jang-Hoon Han, Jin-Hyun Kim and Jeong-Geun Kim  Kwangwoon University, Korea 181                                                                                       |

| CDC(D)-006 | Census Transform Based Stereo Matching Accelerator  Hyeon-Sik Son, Kyeong-ryeol Bae, Seung-Ho Ok and Byungin Moon  Kyungpook National University, Korea 182                                                                                         |

| CDC(D)-007 | Design of multimedia system with Core-A processor Seungpyo Jung and Jusung Park Pusan National University, Korea 183                                                                                                                                |

| CDC(D)-008 | A Fully-Integrated Low Power 24 GHz Radar Transceiver using 110nm CMOS Process  Hyung-Jun Cho, Seong-Kyun Kim, Chenglin Cui and Byung-Sung Kim  Sungkyunkwan University, Korea 184                                                                  |

| CDC(D)-009 | A Design of 77GHz LNA Using 65nm CMOS Process Jun-Young Kim, Seong-Kyun Kim, Chenglin Cui and Byung-Sung Kim Sungkyunkwan University, Korea 185                                                                                                     |

| CDC(D)-010 | Design of 77GHz receiver using on-chip waveguide feeder in 65 nm CMOS Hyeong-Ki Nam, Hyun-Sang Kang, Seong-Kyun Kim, Chenglin Cui and Byung- Sung Kim Sungkyunkwan University, Korea 186                                                            |

| CDC(D)-011 | An 8.7-mW 7-Gb/s CMOS OEIC Receiver                                                                                                                                                                                                                 |

| ·          | Jin-Sung Youn, Myung-Jae Lee, Wang-Soo Kim, Kang-Yeob Park and Woo-Young                                                                                                                                                                            |

| •          | Choi  Yonsei University, Korea                                                                                                                                                                                                                      |

| CDC(D)-012 | A HW-SW Co-Design For A Real-Time Spectral Subtraction Based Noise                                                                                                                                                                                  |

**Cancellation System**

# An 8.7-mW 7-Gb/s CMOS OEIC Receiver

# Jin-Sung Youn, Myung-Jae Lee, Wang-Soo Kim, Kang-Yeob Park, and Woo-Young Choi

Department of Electrical and Electronic Engineering, Yonsei University Seodaemun-gu, Seoul 120-749, Korea wchoi@yonsei.ac.kr

### I. INTRODUCTION

High-performance optoelectronic integrated circuit (OEIC) receivers in CMOS technology have been actively investigated for 850-nm short-distance optical interconnect applications [1-2]. For these applications, low-power operation is strongly required. We present a 7-Gb/s OEIC receiver having an 850-nm Si avalanche photodetector (APD) realized in 65-nm CMOS technology. Our receiver achieves power efficiency of 1.24 mW/Gb/s.

### II. DESCRIPTION

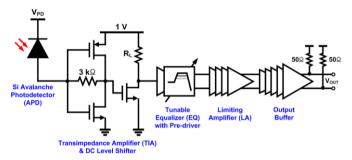

Fig. 1. Simplified block diagram of our CMOS OEIC receiver.

Fig. 1 shows the block diagram of our OEIC receiver. It is composed of a Si APD, a transimpedance amplifier (TIA) with a DC level shifter, a tunable equalizer (EQ) with a single-todifferential amplifier, a limiting amplifier (LA), and an output buffer with  $50-\Omega$  loads. The Si APD is implemented with P<sup>+</sup>/Nwell junction surrounded by shallow trench isolation [3], and its optical-window size is about 10 µm by 10 µm. The TIA is composed of an inverter-based amplifier and a feedback resistance of 3 k $\Omega$ . The inverter-based amplifier can provide much lower power consumption compared to CML-type amplifiers, but in 65-nm CMOS technology its operation speed is limited to about 3 GHz. Single-ended signals at TIA output are converted into fully differential signals with the DC level shifter and the single-to-differential amplifier. The tunable EQ is composed of two-stage of identical cells, and each cell has a differential amplifier with source degeneration and negative capacitance. The LA is composed of four-stage gain cells, and each gain cell is composed of two-stage differential amplifiers with active feedback. The output buffer is used for driving 50- $\Omega$  loads.

# III. CHIP IMPLEMENTAION AND MEASUREMENT RESULTS

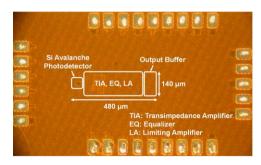

Fig. 2 shows the chip photograph of the fabricated OEIC receiver in 65-nm CMOS technology. The chip area is about 480  $\mu$ m by 140  $\mu$ m. The total power consumption excluding output buffer is about 8.7 mW with 1-V supply voltage.

This work [2012R1A2A1A01009233] was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MEST). The authors are very thankful to IC Design Education Center (IDEC) for EDA software support as well as chip fabrication.

Fig. 2. Chip photograph of the fabricated CMOS OEIC Receiver.

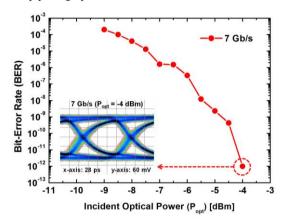

Fig. 3. Measured bit-error rate performance versus incident optical power ( $P_{opt}$ ). Inset shows the measured 7-Gb/s eye diagram.

With the fabricated CMOS OEIC receiver, 7-Gb/s (PRBS 2<sup>31</sup>-1) 850-nm optical data were successfully detected. Fig. 3 shows the measured bit-error rate performance as a function of incident optical power. The inset in Fig. 3 shows the measured eye diagram. Compared to other 850-nm CMOS OEIC receivers reported so far, our receiver has the lowest power efficiency (This work: 1.24 mW/Gb/s, [1]: 6.68 mW/Gb/s, [2]: 11.8 mW/Gb/s).

## REFERENCE

- [1] J.-S. Youn, M.-J. Lee, K.-Y. Park, and W.-Y. Choi, "10-Gb/s 850-nm CMOS OEIC receiver with a silicon avalanche photodetector," *IEEE J. Quantum Electron.* vol. 48, no. 2, pp.229–236. Feb. 2012.

- [2] S.-H. Huang, W.-Z. Chen, Y.-W. Chang, and Y.-T. Huang, "A 10-Gb/s OEIC with meshed spatially-modulated photo detector in 0.18-μm CMOS technology," *IEEE J. Solid-State Circuits* vol. 46, no. 5, pp.1158–1169. May 2011.

- [3] H.-S. Kang, M.-J. Lee, and W.-Y. Choi, "Si avalanche photodetectors fabricated in standard complementary metal-oxide-semiconductor process," *Appl. Phys. Lett.*, vol. 90, no. 15, pp.151118-1–151118-3, Apr. 2007